# Characterization of the C-V Response of Amorphous Indium Gallium Zinc Oxide TFTs

Sangwon Lee, Yongwoo Jeon, Sungchul Kim, Min-Kyung Bae, Dongsik Kong, Yong sik Kim, Hyun Kwang Jung, Dong Myong Kim, and Dae Hwan Kim,<sup>a</sup>

School of Electrical Engineering, Kookmin University, 861-1, Jeongneung-dong, Seongbuk-gu, Seoul, 136-702, KOREA adrlife@kookmin.ac.kr

#### Abstract

The gate-to-source/drain (S/D) capacitance versus the gate voltage (C<sub>G</sub>-V<sub>G</sub>) characteristics of amorphous Indium Gallium Zinc Oxide (a-IGZO) thin film transistors (TFTs) are comprehensively investigated by using normal C<sub>G</sub>-V<sub>G</sub> and quasi-static C<sub>G</sub>-V<sub>G</sub> characteristics. Particularly, under the negatively large V<sub>G</sub>, normal C<sub>G</sub>-V<sub>G</sub> and quasi-static C<sub>G</sub>-V<sub>G</sub> characteristics respond to the gate voltage with each of a different mechanism because of a high hole barrier of S/D contact. Our results strongly suggest that the high hole barrier in S/D contact as well as slow responses of active bulk charge ( $Q_{loc}$  and  $Q_{free}$ ) should be fully considered in order to operate the inversion p-channel a-IGZO TFTs.

#### I. Introduction

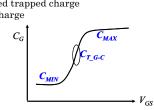

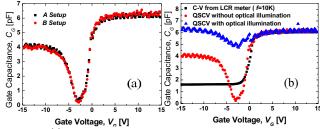

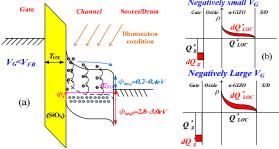

In recent years, amorphous Indium Gallium Zinc Oxide (a-IGZO) thin film transistors (TFTs) are widely attracted as switching devices for active-matrix liquid crystal displays (AMLCDs) and as driving or switching devices for active-matrix organic light-emitting diodes (AMOLEDs) due to the advantages of large scale integration, a low cost room temperature (RT) fabrication process, a high mobility, large area uniformity, and the compatibility with transparent and electronic paper applications [1, 2]. To make a-IGZO TFTs affordable for various innovative and practical applications, the mechanism of gate capacitance-gate voltage (C<sub>G</sub>-V<sub>G</sub>) characteristics, indispensible for the design of circuits and systems, should be fully understood. In commonly observed C<sub>G</sub>-V<sub>G</sub> curves (measured by using LCR meter with gate-to-grounded source/drain (S/D) terminals) in n-channel TFTs integrated in n-type a-IGZO films, C<sub>G</sub> becomes saturated to C<sub>MIN</sub>, as shown in Fig. 1(a) with negatively larger V<sub>G</sub>. As generally accepted, a-IGZO TFTs are difficult to operate in an inversion p-channel mode, which may be attributed to high subgap density-of-states (DOS) near valence band maximum (VBM: E<sub>V</sub>) in a-IGZO film [3]. However, why  $C_{\text{MIN}}$  is unaffected by  $V_{\text{G}}$  has not yet been completely clarified. Motivated by these viewpoints, in this work, C<sub>G</sub>-V<sub>G</sub> curves of a-IGZO TFTs are characterized, including the channel length (L), width (W) and measurement dependences.

#### **II. Device Structure**

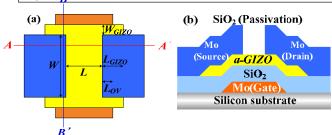

The device structure used in this work is of the inverted staggered type which is the most commonly used structure for AMLCD (as shown in Fig. 1). Devices are fabricated as follows: On a thermally grown SiO<sub>2</sub>/Si substrate, the first sputtered deposition at RT and patterning of molybdenum (Mo) gate are followed by plasma-enhanced chemical vapor deposition (PECVD) of SiO<sub>2</sub>  $(T_{OX}=100 \text{ nm})$  at 300 °C. An a-IGZO film  $(In_2O_3:Ga_2O_3: ZnO=2:2:1$ at %) is then sputtered by RF magnetron sputtering at RT in a mixed Ar/O<sub>2</sub> (100:1 at sccm) and wet-etched with diluted HF to get the pattern of 70-nm-thick active layer ( $T_{IGZO}$ =70 nm). To form S/D electrode, a 200-nm-thick layer of Mo is sputtered at RT and then patterned by dry-etching. After N2O plasma treatment, a SiO2 passivation layer is continuously deposited at 150 °C by PECVD without a vacuum break.

## III. Characterization of C-V Characteristics

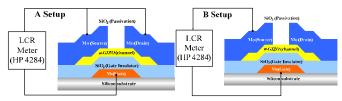

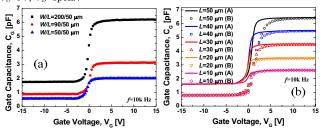

The device parameters are shown in Fig. 1(a) and Table I: the channel length (L), channel width (W), the width of the region between gate and a-IGZO active layer ( $W_{IGZO}$ ), the length of the region between S/D and a-IGZO active layer ( $L_{IGZO}$ ), and the length of overlap region between gate and S/D ( $L_{OV}$ ).  $W_{IGZO}$ =5 µm,  $L_{IGZO}$ =15 µm, and  $L_{OV}$ =10 µm are commonly used. Fig. 2 shows two kinds of the C-V measurement setups (A and B). Fig. 3 shows the W, L, and measurement setup-dependence of C-V curve from LCR

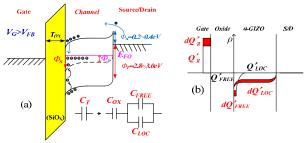

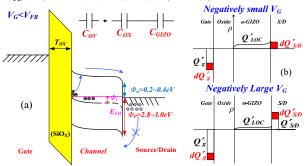

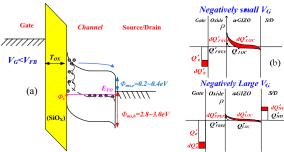

meter (Agilent 4284A). Whereas the maximum value of C-V curve  $(C_{MAX})$  is dependent not on measurement setup but on L and W, the minimum value of C-V curve (C<sub>MIN</sub>) is dependent not on L but on measurement setup and W. As the result of calculating the C-V characteristic model equations in Table I, it is found that C<sub>MAX</sub> is consistent with (1) and C<sub>MIN</sub> is with (2) which is determined only by the gate-to-S/D overlap region. Extracted model parameters are  $W_0$ =5.9,  $L_0$ =5.3,  $W_I$ =10, and  $L_I$ =4.3 $\mu$ m, respectively. Fig. 5 and 6 illustrate the mechanism on the C-V characteristics in Fig. 3 (C-V curve from LCR meter). As V<sub>G</sub> positively increases, Fermi-level E<sub>F</sub> approaches to E<sub>C</sub> with energy band bending and the free electrons are injected to a-IGZO active layer from S/D contact, shown in Fig. 5(a). Some of the injected electrons are trapped in subgap DOS of a-IGZO active channel layer. The others exist as the free charges in conduction band and contribute to DC current (I-V) and/or AC current (C-V), as shown in Fig. 5(b). Both the electrons respond to a small signal in  $V_G$ , resulting in the C-V curve modulated by  $V_G$ . Under positively large V<sub>G</sub>, free charges in conduction band dominantly respond to a small signal, as is the case of covalent Si. Consequently, C<sub>MAX</sub> is saturated to C<sub>OX</sub> because the C<sub>FREE</sub> is very large. However, under negative V<sub>G</sub>, the charge in active channel is not well modulated by V<sub>G</sub> because holes are hard to be injected from S/D contact due to much higher hole barrier height  $(\Phi_P)$  than that of electron ( $\Phi_E$ ), as shown in Fig. 6. The  $\Phi_E$  of a-IGZO TFTs with Mo S/D metal is about 0.2~0.4 eV in literature [3, 4]. Considering bandgap of a-IGZO active layer,  $\Phi_P$  is to be 2.8~3.0 eV. Therefore, C<sub>MIN</sub> is characterized to be (2), and the C<sub>MIN</sub> in setup B is a half value of that in setup A (as seen in Fig. 3(b)) because the area of gate-S/D overlap region becomes a half. On the other hand, Fig. 4 shows the quasi-static C-V (QSCV) curve measured by Semiconductor Parameter Analyzer (4156C) [5]. Under negative V<sub>G</sub>, clear discrepancy is found between QSCV and C-V curve in LCR meter (Fig. 4(b)) and the QSCV curve is independent of measurement setup (Fig. 4(a)). Because the gate current is integrated in QSCV (like low-frequency C-V) while the impedance is monitored in LCR meter (like high-frequency C-V), the ionized donor-like DOS by subgap state-assisted free electron generation (electron detrapping to E<sub>C</sub>) is monitored only in QSCV case, as shown in Fig. 7(a), leading to the V<sub>G</sub>-dependent C<sub>G</sub> under negative V<sub>G</sub>. As V<sub>G</sub> becomes negatively larger, the subgap state-assisted generation becomes such unlikely that C<sub>G</sub> results to be saturated (Fig. 7(b) and 4(b)). Under optical illumination, the C<sub>G</sub> under negative V<sub>G</sub> approaches to C<sub>OX</sub> (Fig. 4(b)) because the subgap state-assisted generation becomes more activated (Fig. 8). Therefore, in order to design a practical p-channel AOS TFTs, lower  $\Phi_P$ between AOS active and S/D metal as well as shallow acceptor in AOS active (e.g., SnO or CuO) should be fully considered.

The mechanism on C-V characteristics of a-IGZO TFTs is comprehensively investigated. C<sub>MIN</sub> is determined only by the gate-S/D overlap region. Under negative V<sub>G</sub>, the active channel charge is not well modulated due to both the slow response of trapping/detrapping dynamics of subgap DOS and a high  $\Phi_P$ . In addition, the discrepancy between QSCV and C-V curve in LCR meter and the photo-response of C-V curve are consistently explained.

### Acknowledgements

This work was supported by the Korea Science and Engineering Foundation (KOSEF) grant funded by the Korea government (MEST) (No. 2009-0080344).

#### References

- [1] J. K. Jeong et al., Int. Symp. Dig.Tech-Soc. Information Display (2008)

- [2] J.-H. Lee et al., Int. Symp. Dig. Tech. papers-Soc. Information Display 625 (2008)

- [3] Kichan Jeon et al., Appl. Phys. Lett. 93. 182102 (2008)

[4] Ihun Song et al., IEEE Electron Device Lett. 29, 549 (2008)

[5]Agilent application note 4156-10: evaluation of gate oxides using a voltage step

## Table I. The C-Vcharacteristic model equations

$$W_{eff OV,G-S/D} = W + 2 \times W_1, L_{eff OV,G-S/D} = L_{OV} + L_1$$

(5)

$$C_{T\_G-C} = C_T \times W_{eff\_G-C} \times L_{eff\_G-C}$$

$$(6)$$

$$C_T = \frac{C_{OX} \times C_B}{C_{OX} + C_B}, C_B = C_{LOC} + C_{FREE}$$

$$(7)$$

$$Q_{LOC} = q \int_{E_F}^{E_F} \int_{x=0}^{\alpha = T_{GEO}} g(E) \times f(E) dE dx$$

(8)

$$Q_{FREE} = q \int_{x=0}^{x=T_{GIBO}} N_C \exp\left(-\frac{E_C - E_F}{KT}\right) dx$$

(9)

$$C_{LOC} = \frac{\partial Q_{LOC}}{\partial \phi_s}, C_{FREE} = \frac{\partial Q_{FREE}}{\partial \phi_s}$$

$$C_{CX}/C_{OV}$$

: Gate oxide insulator/overlap capacitance per unit area

$C_{OX}/C_{OV}$ : Gate oxide insulator/overlap capacitance per unit area  $W_{eff,G}$   $_{C}/L_{eff,G}$   $_{C}$ : Effective channel width/length

$W_0$  / $L_0$ : Characteristic channel width / length describing the fringing field effect between gate and channel

fringing field effect between gate and channel  $W_{eff\_OV,G\_S/D}/L_{eff\_OV,G\_S/D}$ : Effective overlap width/length

$W_1/L_1$ : Characteristic overlap width/length describing the fringing field effect between gate and S/D

$C_{T GC}$ : Total gate capacitance

$C_T$ : Total gate capacitance per unit area

$C_B$ : Capacitance due to  $V_G$  responsive total charge

CLOC: Capacitance due to localized trapped charge

$C_{FREE}$ : Capacitance due to free charge

g(E): DOS of a-IGZO active layer

f(E): Fermi-Dirac distribution function

$N_C$ : Conduction band effective DOS

$E_C$ : Conduction band minimum  $E_V$ : Valence band maximum

Fig. 1. (a) Schematic top view , (b) A-A' and (c) B-B' cross sectional view of a-IGZO TFTs.

Fig. 2. Two kinds of C-V measurement setups. A ( $V_D$ = $V_S$ =0V) and B ( $V_S$ =0V,  $V_D$ =open).

Fig. 3. (a)  $W\!/\!L$  and (b)  $L\!/\!$  measurement setup-dependence of  $C\!-\!V$  curves.

Fig. 4. (a) Measurement setup-dependence of QSCV curve from Semiconductor Parameter Analyzer (HP 4156C), (b) Comparison between C-V curve form LCR meter (HP 4284) and QSCV curve from Semiconductor Parameter Analyzer (HP 4156C).

Fig. 5. (a) Energy band diagram and its equivalent capacitance model, (b) the charge density in gate-source/drain overlap region under  $V_G > V_{FB}$  for C-V curve from LCR meter (HP 4284).

Fig. 6. (a) Energy band diagram and its equivalent capacitance model, (b) the charge density in negatively small/large  $V_G$  under  $V_G < V_{FB}$  for C-V curve from LCR meter (HP 4284).

Fig.7. (a) Energy band diagram and (b) the charge density in negatively small/large  $V_G$  under  $V_{C}\!\!<\!V_{FB}$  for QSCV curve from Semiconductor Parameter Analyzer (HP 4156C) without an optical illumination.

Fig. 8. (a) Energy band diagram and (b) the charge density in negatively small/large  $V_G$  under  $V_G < V_{FB}$  for QSCV curve from Semiconductor Parameter Analyzer (HP 4156C) with an optical illumination.